Что такое PCI Express

PCI Express

(

Peripheral Component Interconnect Express

, сокращенно —

PCIe

или

PCI-e

) — это компьютерная шина, использующая высокопроизводительный протокол последовательной передачи данных. Большинству непосвященных это определение наверняка покажется туманным. Чтобы стало понятней, разберем его более подробно. Компьютерная шина — соединение, служащее для передачи данных между функциональными блоками компьютера. Протокол – в данном случае значит «схема», «алгоритм», «порядок». Последовательная передача данных – понятие более сложное, ему придется уделить больше внимания. Все данные внутри компьютера циркулируют, обрабатываются и хранятся в виде двоичного кода, мельчайшими частичками которого являются биты. Подробнее об этом можно узнать здесь. Передача данных между функциональными блоками компьютера может осуществляться либо

параллельным

, либо

последовательным

способом.

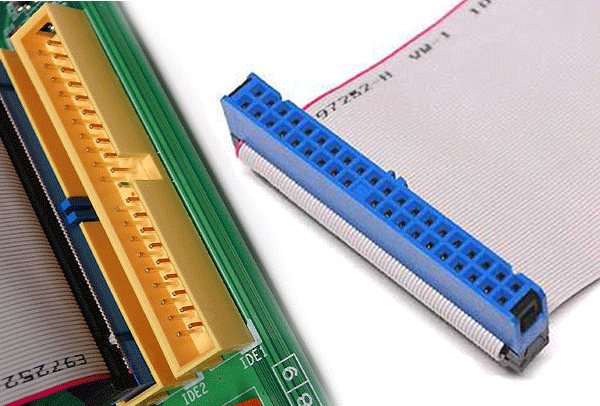

Параллельная передача данных

Параллельный способ подразумевает использование физического соединения из значительного количества проводников. Передача данных осуществляется «порциями», в которых количество битов соответствует количеству проводников в соединении. Каждая такая порция перед передачей как бы «развертывается в пространстве», разделяясь на биты, каждый из которых проходит к принимающему устройству по отдельному проводнику. Таким образом, каждую единицу времени каждый бит двоичного кода передается по отдельному проводу этого соединения, одновременно (параллельно) с другими битами, передающимися по остальным его проводам. Поэтому схема и называется параллельной. Например, компьютерная шина PATA (IDE), которая в домашних компьютерах не так давно была основным способом подключения жестких дисков, состоит из 40 проводников (на изображении ниже). Из них только 16 используются непосредственно для параллельной передачи данных. За каждую передачу (такт) по такой шине проходит 16 битов информации. Частота шины — 33 МГц, то есть каждую секунду происходит 33 млн. передач. Таким образом, максимальная пропускная способность такого соединения равна 528 млн. битов в секунду (16 х 33 млн.), или, если перевести в мегабайты — 66 Мегабайт / с.

Несмотря на простоту, параллельная передача данных изжила себя и уже почти не используется в компьютерной технике. Главные ее недостатки: • высокие затраты на создание каналов (нужно много проводников); • высокая помеховосприимчивость из-за взаимного влияния передаваемых сигналов друг на друга (особенно, на длинные расстояния); • необходимость обеспечения синхронного прохождения данных одновременно по всех проводниках соединения, из-за чего достижение высокой частоты отправки сигналов (частоты шины) является слишком сложной задачей.

Последовательная передача данных

Влиянию указаных выше негативных факторов в значительно меньшей степени подвержены схемы последовательной передачи данных. Сегодня они являются очень распространенными. Все USB-устройства, современные жесткие диски, SSD, видеокарты, сетевые карты и т.д. взаимодействуют с другим оборудованием с использованием последовательной передачи данных. Способ ее реализации в каждом из этих видов устройств, конечно же, отличается, но принцип везде одинаков. Для последовательной схемы не нужно много проводников. Передача данных осуществляется через один коммуникационный канал по одному биту за каждую передачу, последовательно, один за одним (что-то на подобие азбуки Морзе). На первый взгляд, такая схема кажется менее эффективной, чем в случае с параллельной передачей. Но это далеко не так. Высокая скорость здесь достигается за счет огромной частоты передачи данных (несколько миллиардов в секунду). А для устройств, требующих особо высоких скоростей обмена данными, одновременно используется несколько таких каналов (линий). Например, современные игровые видеокарты подключаются к компьютеру через 16 линий PCIe (PCIe x16).

Разъем кабеля USB

| № | Сигнал | № | Сигнал |

| A1 | Vcc | B1 | Vcc |

| A2 | Port0 data+ | B2 | Port1 data+ |

| A3 | Port0 data- | B3 | Port1 data- |

| A4 | GND | B4 | GND |

Особенности стандарта PCI Express, его версии

Разработка стандарта PCI Express была начата фирмой Intel. Спецификации первой его версии появились еще в 2002 году. Сейчас развитием PCI Express занимается организация PCI Special Interest Group, в совет директоров которой входят представители основных разработчиков аппаратного и программного обеспечения (Intel, Microsoft, IBM, AMD, Sun Microsystems, HP, NVIDIA и другие). В своем развитии PCIe прошел несколько этапов и уже развился до версии 5.0. PCIe является полнодуплексным

протоколом, то есть предусматривает использование независимых друг от друга каналов приёма и передачи данных (устройство может одновременно отправлять и получать данные). Перед отправкой данные кодируются в блоки. Это необходимо для синхронизации передающего и принимающего устройств, а также уменьшения влияния помех. В версиях PCIe 1.0 и PCIe 2.0 используется схема кодирования

8b/10b

. То есть, каждый 8-битный блок кодируется в 10-битный, в котором только 80% передаваемых данных являются полезными. Остальные 20% нужны для обеспечения правильной работы протокола. В PCIe 3.0 и боле новых ее версиях данные кодируются по более эффективной схеме

128b/130b

(каждые 128 бит кодируются в 130-битный блок). Доля полезного содержания в передаваемых данных здесь составляет уже около 98,46%. Разные версии PCIe отличаются не только способом «упаковки» битов в блоки, но и частотой передачи данных. В PCIe 1.0 она составляет 2,5 ГТ/с (гигатранзакций в секунду), то есть за одну секунду передается 2,5 миллиарда битов. Для лучшего восприятия переведем это в привычные единицы:

2,5*109 Бит / с = 312,5 Мегабайт / с.

Учитывая, что только 80% из них являются полезными данными, реальная пропускная способность PCIe 1.0 составляет 250 Мегабайт / с. В PCIe 5.0 частота передачи данных возросла аж до 32 ГТ/с. Переведем это в удобный вид:

32*109 Бит / с = 4000 Мегабайт / с = 4 Гигабайт / с.

Поскольку полезные данные составляют 98,46%, реальная пропускная способность PCIe 5.0 равна 3,938 Гигабайт / с. Подробнее об особенностях разных версиях PCIe см. в таблице:

| Версия PCI Express | Год выхода | Схема кодирования | Скорость передачи | Пропускная способность на x линий: | |||

| x1 | x4 | x8 | x16 | ||||

| PCIe 1.0 | 2002 | 8b/10b | 2,5 ГТ/с | 250 Мб/с | 1 Гб/с | 2 Гб/с | 4 Гб/с |

| PCIe 2.0 | 2007 | 8b/10b | 5 ГТ/с | 500 Мб/с | 2 Гб/с | 4 Гб/с | 8 Гб/с |

| PCIe 3.0 | 2010 | 128b/130b | 8 ГТ/с | 984,6 Мб/с | 3,94 Гб/с | 7,88 Гб/с | 15,8 Гб/с |

| PCIe 4.0 | 2017 | 128b/130b | 16 ГТ/с | 1,969 Гб/с | 7,88 Гб/с | 15,8 Гб/с | 31,5 Гб/с |

| PCIe 5.0 | 2019 | 128b/130b | 32 ГТ/с | 3,938 Гб/с | 15,75 Гб/с | 31,5 Гб/с | 63 Гб/с |

Разъем питания приводов

| № | Сигнал | Цвет |

| 1 | +12В | желтый |

| 2 | корпус | черный |

| 3 | корпус | черный |

| 4 | +5В | красный |

Применение PCI Express в компьютере. Разъемы PCI Express

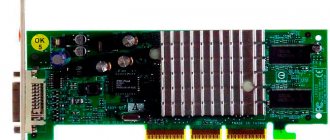

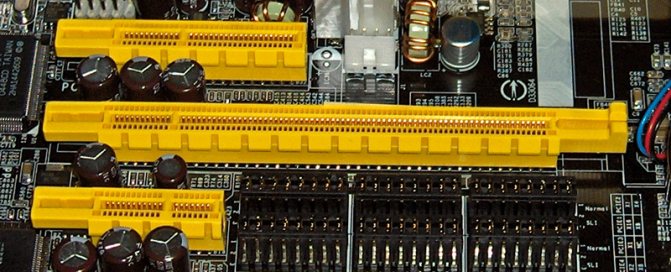

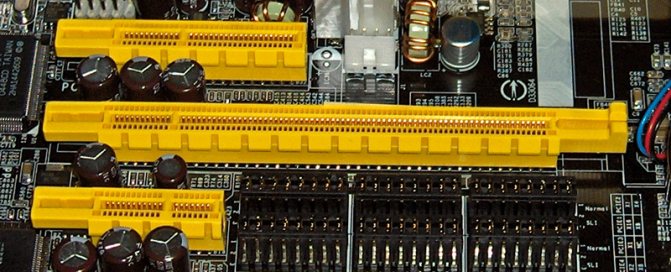

Контроллер (управляющее устройство) линий PCIe не так давно встраивался только в чипсет (главную микросхему) материнской платы. Но, начиная с 2009 года, контроллер PCIe добавляется производителями также и непосредственно в центральный процессор. Это уменьшает задержки и позволяет процессору более эффективно взаимодействовать с другими устройствами. Версии и количество линий PCIe в разных моделях процессоров и чипсетов отличается. Бо́льшая их часть формируется в разъемы, размещаемые на материнской плате. Они позволяют подключать к компютеру разнообразные устройства (видеокарты, звуковые карты, сетевые карты, Wi-Fi-адаптеры и др.). На материнской плате современного компьютера можно найти разъемы PCIe нескольких видов, отличающихся количеством используемых в них линий PCIe (от х1 до х16 линий). Не зависимо от того, насколько старым является компьютер, и какая версия PCIe в нем используется, эти разъемы всегда выглядят одинаково:

на изображении: верхний разъем — PCIe x4, по средине — PCIe x16, внизу — PCIe x1

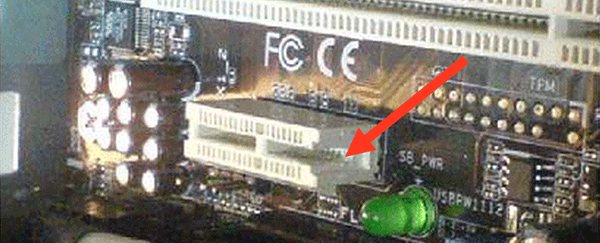

Разные версии PCIe являются полностью совместимыми. То есть, если в старый компьютер, где используется версии PCIe 2.0, установить, например, видеокарту с PCIe 4.0, она будет нормально работать. Однако, реальная скорость обмена данными при этом у нее будет ограничена возможностями PCIe 2.0. И наоборот, в самый новый компьютер с PCIe 4.0 можно без проблем установить старую видеокарту с PCIe 2.0. Еще одной особенностью PCIe является совместимость разных ее разъемов. В разъем PCIe x16 можно подключить не только видеокарту, но и абсолютно любое другое устройство PCIe, в том числе и с разъемом PCIe x8, PCIe x4 или PCIe x1. Совместимость разъемов сохраняется также и в обратную сторону. То есть, в разъем PCIe x1 можно установить видеокарту с разъемом PCIe x16. Физически она туда не войдет, но если разрезать заднюю стенку разъема (как на изображении ниже), то все получится. Это, конечно же, «кустарщина» и без крайней надобности так делать не нужно. Тем более, что видеокарта при таком подключении будет работать в режиме PCIe x1, что весьма негативно скажется на ее быстродействии.

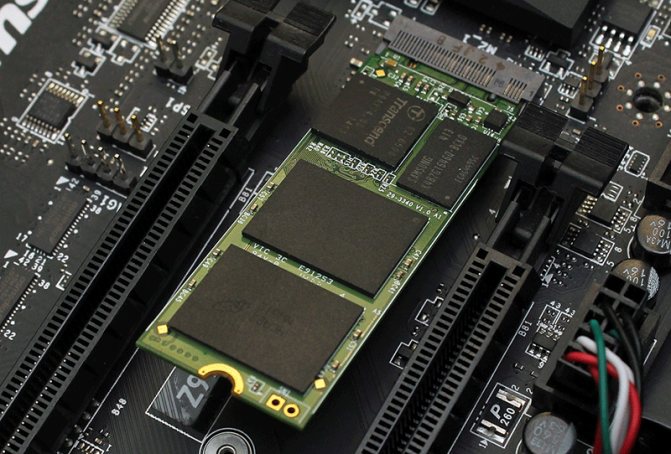

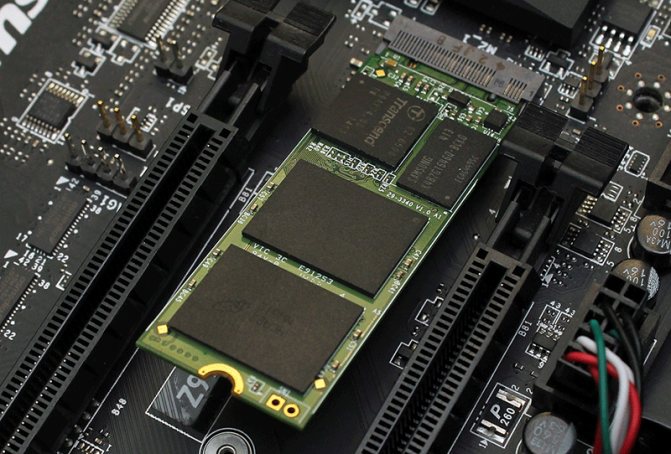

В ноутбуках для установки дополнительных устройств вместо упомянутых выше разъемов используется более компактный вариант — Mini PCIe. Линии PCIe используются также для создания некоторых других разъемов, в чатности, разъемов M.2 (служат для подключения современных запоминающих устройств, а также устройств некоторых других типов).

на изображении — разъем M.2 с запоминающим устройством в нем

Слоты расширения материнской платы

(не совсем про кабели, но пригодится)

8ми битный слот

| Сторона монтажа | Сторона пайки | ||||

| № | Сигнал | Значение | № | Сигнал | Значение |

| A1 | I/O CH CK | Контроль канала ввода-вывода | B1 | GND | Земля |

| A2 | D7 | Линия данных 8 | B2 | RES DRV | Сигнал Reset |

| A3 | D6 | Линия данных 7 | B3 | +5V | +5В |

| A4 | D5 | Линия данных 6 | B4 | IRQ2 | Запрос прерывания 2 |

| A5 | D4 | Линия данных 5 | B5 | -5V | -5В |

| A6 | D3 | Линия данных 4 | B6 | DRQ2 | Запрос DMA 2 |

| A7 | D2 | Линия данных 3 | B7 | -12V | -12В |

| A8 | D1 | Линия данных 2 | B8 | RES | Зарезервировано |

| A9 | D0 | Линия данных 1 | B9 | +12V | +12В |

| A10 | I/O CN RDY | Контроль готовности канала ввода-вывода | B10 | GND | Земля |

| A11 | AEN | Adress Enable, контроль за шиной при CPU и DMA-контроллере | B11 | MEMW | Данные записываются в память |

| A12 | A19 | Адресная линия 20 | B12 | MEMR | Данные считываются из памяти |

| A13 | A18 | Адресная линия 19 | B13 | IOW | Данные записываются в I/O порт |

| A14 | A17 | Адресная линия 18 | B14 | IOR | Данные читаются из I/O порта |

| A15 | A16 | Адресная линия 17 | B15 | DACK3 | DMA-Acknowledge (подтверждение) 3 |

| A16 | A15 | Адресная линия 16 | B16 | DRQ3 | Запрос DMA 3 |

| A17 | A14 | Адресная линия 15 | B17 | DACK1 | DMA-Acknowledge (подтверждение) 1 |

| A18 | A13 | Адресная линия 14 | B18 | IRQ1 | Запрос прерывания 1 |

| A19 | A12 | Адресная линия 13 | B19 | REFRESH | Регенерация памяти |

| A20 | A11 | Адресная линия 12 | B20 | CLC | Системный такт 4,77 МГц |

| A21 | A10 | Адресная линия 11 | B21 | IRQ7 | Запрос прерывания 7 |

| A22 | A9 | Адресная линия 10 | B22 | IRQ6 | Запрос прерывания 6 |

| A23 | A8 | Адресная линия 9 | B23 | IRQ5 | Запрос прерывания 5 |

| A24 | A7 | Адресная линия 8 | B24 | IRQ4 | Запрос прерывания 4 |

| A25 | A6 | Адресная линия 7 | B25 | IRQ3 | Запрос прерывания 3 |

| A26 | A5 | Адресная линия 6 | B26 | DACK2 | DMA-Acknowledge (подтверждение) 2 |

| A27 | A4 | Адресная линия 5 | B27 | T/C | Terminal Count, сигнализирует конец DMA-трансформации |

| A28 | A3 | Адресная линия 4 | B28 | ALE | Adress Latch Enabled, расстыковка адрес/данные |

| A29 | A2 | Адресная линия 3 | B29 | +5V | +5В |

| A30 | A1 | Адресная линия 2 | B30 | OSC | Частота тактового генератора 14,31818 МГц |

| A31 | A0 | Адресная линия 1 | B31 | GND | Земля |

16ти битный слот

| Сторона монтажа | Сторона пайки | ||||

| № | Сигнал | Значение | № | Сигнал | Значение |

| A1 | I/O CH CK | Контроль канала ввода-вывода | B1 | GND | Земля |

| A2 | D7 | Линия данных 8 | B2 | RES DRV | Сигнал Reset |

| A3 | D6 | Линия данных 7 | B3 | +5V | +5В |

| A4 | D5 | Линия данных 6 | B4 | IRQ9 | Каскадирование второго контроллера прерываний |

| A5 | D4 | Линия данных 5 | B5 | -5V | -5В |

| A6 | D3 | Линия данных 4 | B6 | DRQ2 | Запрос DMA 2 |

| A7 | D2 | Линия данных 3 | B7 | -12V | -12В |

| A8 | D1 | Линия данных 2 | B8 | RES | Коммуникация с памятью без времени ожидания |

| A9 | D0 | Линия данных 1 | B9 | +12V | +12В |

| A10 | I/O CN RDY | Контроль готовности канала ввода-вывода | B10 | GND | Земля |

| A11 | AEN | Adress Enable, контроль за шиной при CPU и DMA-контроллере | B11 | SMEMW | Данные записываются в память (до 1М байта) |

| A12 | A19 | Адресная линия 20 | B12 | SMEMR | Данные считываются из памяти (до 1 Мбайта) |

| A13 | A18 | Адресная линия 19 | B13 | IOW | Данные записываются в I/O порт |

| A14 | A17 | Адресная линия 18 | B14 | IOR | Данные читаются из I/O порта |

| A15 | A16 | Адресная линия 17 | B15 | DACK3 | DMA-Acknowledge (подтверждение) 3 |

| A16 | A15 | Адресная линия 16 | B16 | DR Q3 | Запрос DMA 3 |

| A17 | A14 | Адресная линия 15 | B17 | DACK1 | DMA-Acknowledge (подтверждение) 1 |

| A18 | A13 | Адресная линия 14 | B18 | IRQ1 | Запрос IRQ 1 |

| A19 | A12 | Адресная линия 13 | B19 | REFRESH | Регенерация памяти |

| A20 | A11 | Адресная линия 12 | B20 | CLC | Системный такт 4,77 МГц |

| A21 | A10 | Адресная линия 11 | B21 | IRQ7 | Запрос IRQ 7 |

| A22 | A9 | Адресная линия 10 | B22 | IRQ6 | Запрос IRQ 6 |

| A23 | A8 | Адресная линия 9 | B23 | IRQ5 | Запрос IRQ 5 |

| A24 | A7 | Адресная линия 8 | B24 | IRQ4 | Запрос IRQ 4 |

| A25 | A6 | Адресная линия 7 | B25 | IRQ3 | Запрос IRQ 3 |

| A26 | A5 | Адресная линия 6 | B26 | DACK2 | DMA-Acknowledge (подтверждение) 2 |

| A27 | A4 | Адресная линия 5 | B27 | T/C | Terminal Count, сигнализирует конец DMA-трансформации |

| A28 | A3 | Адресная линия 4 | B28 | ALE | Adress Latch Enabled, расстыковка адрес/данные |

| A29 | A2 | Адресная линия 3 | B29 | +5V | +5В |

| A30 | A1 | Адресная линия 2 | B30 | OSC | Такт осциллятора 14,31818 МГц |

| A31 | A0 | Адресная линия 1 | B31 | GND | Земля |

| C1 | SBHE | System Bus High Enabled, сигнал для 16-разрядных данных | D1 | MEM CS 16 | Memory Chip Select (выбор) |

| C2 | LA23 | Адресная линия 24 | D2 | I/O CS 16 | I/O карта с 8 бит/16 бит переносом |

| C3 | LA22 | Адресная линия 23 | D3 | IRQ10 | Запрос прерывания 10 |

| C4 | LA21 | Адресная линия 22 | D4 | IRQ11 | Запрос прерывания 11 |

| C5 | LA20 | Адресная линия 21 | D5 | IRQ12 | Запрос прерывания 12 |

| C6 | LA19 | Адресная линия 20 | D6 | IRQ15 | Запрос прерывания 15 |

| C7 | LA18 | Адресная линия 19 | D7 | IRQ14 | Запрос прерывания 14 |

| C8 | LA17 | Адресная линия 18 | D8 | DACK0 | DMA-Acknowledge (подтверждение) 0 |

| C9 | MEMR | Чтение данных из памяти | D9 | DRQ0 | Запрос DMA 0 |

| C10 | MEMW | Запись данных в память | D10 | DACK5 | DMA-Acknowledge (подтверждение) 5 |

| C11 | SD8 | Линия данных 9 | D11 | DRQ5 | Запрос DMA 5 |

| C12 | SD9 | Линия данных 10 | D12 | DACK6 | DMA-Acknowledge (подтверждение) 6 |

| C13 | SD10 | Линия данных 11 | D13 | DRQ6 | Запрос DMA 6 |

| C14 | SD11 | Линия данных 12 | D14 | DACK7 | DMA-Acknowledge (подтверждение) 7 |

| C15 | SD12 | Линия данных 13 | D15 | DRQ7 | Запрос DMA 7 |

| C16 | SD13 | Линия данных 14 | D16 | +5V | +5В |

| C17 | SD14 | Линия данных 15 | D17 | MASTER | Сигнал Busmaster |

| C18 | SD15 | Линия данных 16 | D18 | GND | Земля |

Нужно ли апгрейдить компьютер ради PCIe 4.0

Как уже говорилось выше, последней из официально вышедших версий PCIe является версия 5.0 (опубликованы официальные спецификации, но на практике она не используется). Самой «свежей» версией из используемых по состоянию на конец 2022 года является PCIe 4.0, и, судя по всему, еще долго будет таковой оставаться. Она вышла в 2017 году, однако внедрена в конкретные устройства лишь недавно, в 2019 году. Ее начала использовать компания AMD в процессорах Ryzen архитектуры Zen 2, а также в видеокартаx Radeon серии RX 5700 / 5500. Несомненно, это значительное достижение AMD, однако, оно пока является лишь заделом на будущее и не дает никаких практических преимуществ перед конкурентами. Компания Intel внедрять PCIe 4.0 в свои процессоры не торопится. Не спешит делать это и компания nVidia, видеокарты которой пока довольствуются PCIe 3.0. Все дело в том, что на современном этапе развития компьютерной техники возможностей PCIe 3.0 вполне достаточно. Превосходство PCIe 4.0 можно увидеть лишь в синтетических тестах. В практических же сценариях необходимости в настолько высоких скоростях обмена данными пока нет. Видеокарты с PCIe 4.0 вполне нормально работают и в системах с PCIe 3.0. Более того, даже в компьютерах с PCIe 2.0 они показывают почти такую же производительность в играх и других приложениях, как в компьютерах с PCIe 4.0. Но продлится это, судя по всему, не долго. Направлением, где в ближайшее время станет реально востребованной PCIe 4.0, являются современные М.2 SSD-накопители, быстродействие которых уже почти «уперлось в потолок » стандарта PCIe 3.0. Затем черед дойдет до видеокарт и другого оборудования. Так что апгрейдить старый компьютер только ради PCIe 4.0 пока нецелесообразно. Однако при покупке нового компьютера, который планируется к использованию достаточно длительнное время, брать во внимание версию PCIe, поддерживаемую его внутренними устройствами, однозначно нужно.

Разъемы для подключения клавиатуры

Внимание! контакты нумеруются не по кругу, обращайте внимание на цифру, стоящую возле контакта.

| DIN5 | PS/2 | |

| № | Сигнал | Назначение |

| 1 | Тактовая частота | Выход |

| 2 | Линия данных | Вход/Выход |

| 3 | Сброс | — |

| 4 | Корпус | Вход |

| 5 | +5В | Вход |

| Сигнал | Вход/Выход | |

| 1 | Линия данных | Вход/Выход |

| 2 | Не подключен | Резерв |

| 3 | Корпус | Вход |

| 4 | +5В | Вход |

| 5 | Тактовая частота | Выход |

| 6 | Не подключен | Резерв |

самостоятельно(нестандартно)подключение видеокарты кноутбуку

Добрый вечер. Извенясь что долго не писал, просто уезжал в другой город. Так вот возвращаясь к своей теме, хочу сказать что я нашел даташит на 910GML, и внём еть подходящие (по моему мнению) сигналы. Я нашел от 0до 15 линии трансмиттеров и рессиверов,(то что надо для видеокарты с разьёмом PCI Express X16). Но сталкнулся с одной проблемкой. В даташите я неувидел некаторые сигналы,а именно (PRSNT1# (PRSNT2#(PWRGD(REFCLK+(REFCLK-(JTAG3(JTAG4) ГДЕ ЭТИ СИГНАЛЫ находятся на чипе 910GML, Я хотел у вас спросить. У всех может помочь. Ниже,если у меня получится ,я вложу рисунок-схему разьёма PCI-E16. С выводами (какие есть) у видеокарты Radeon HD 2600 512Mb GDDR-2. Красная линия — есть контакт, синяя линия — нет контакта, Знак вопроса — контакт на видеокарточке есть —но в даташите мною ненайден.

ДОБАВЛЕНО 11/02/2009 22:11

Вот рисунок-схема. pcie-slot-big(отсутствующие контакты как и HD2600.gif»

ДОБАВЛЕНО 11/02/2009 22:28

ДОБАВЛЕНО 11/02/2009 22:55

Пришлось урезать рисунок,иначе я не мог его вставить.Попытаюсь вложить ещё вырезку с даташита 910GML,если получится, со всеми сигналами. Подскажите,или хоть намекните «в какой степи» искать недостающие сигналы. И ещё вопросик,если можно. Какая ёмкость у конденсаторов 32шт,каторые идут по сигналам к разьёму PCIe x16 ? (104Пф. или это их номер?) И нужны они там или нет? И ещё,какие из ненайденых мной сигналов нужны обязательно,(что-бы карта работала и видел её ноутбук), а какими можно пренебречь? Заранее благодарен вашему ответу !

Ответ или здесь, или мой мейл

pcie-slot-big(отсутствующие контакты как и HD2600.gif 73.11 КБ

Скачано: 9372 раз(а)

Добрый день. Никак не получалось вставить вырезку с таблицей сигналов. PCI Express Based Graphics / Serial Digital Video Out Receive Signal Group E30- EXP_RXN0 SDVO_TVCLKIN# F34- EXP_RXN1 SDVOB_INT# G30- EXP_RXN2 SDVO_FLDSTALL# H34- EXP_RXN3 J30- EXP_RXN4 K34- EXP_RXN5 SDVOB_INT# L30- EXP_RXN6 M34- EXP_RXN7 N30- EXP_RXN8 P34- EXP_RXN9 R30- EXP_RXN10 T34- EXP_RXN11 U30- EXP_RXN12 V34- EXP_RXN13 W30- EXP_RXN14 Y34- EXP_RXN15 D30- EXP_RXP0 SDVO_TVCLKIN E34- EXP_RXP1 SDVOB_INT F30- EXP_RXP2 SDVO_FLDSTALL G34- EXP_RXP3 H30- EXP_RXP4 J34- EXP_RXP5 SDVOB_INT K30- EXP_RXP6 L34- EXP_RXP7 M30- EXP_RXP8 N34- EXP_RXP9 P30- EXP_RXP10 R34- EXP_RXP11 T30- EXP_RXP12 U34- EXP_RXP13 V30- EXP_RXP14 W34- EXP_RXP15 Table 13-17. PCI Express Based Graphics / Serial Digital Video Out Transmit Signal Group E32 EXP_TXN0 D32 EXP_TXP0 F36 EXP_TXN1 E36 EXP_TXP1 G32 EXP_TXN2 F32 EXP_TXP2 H36 EXP_TXN3 G36 EXP_TXP3 J32 EXP_TXN4 H32 EXP_TXP4 K36 EXP_TXN5 J36 EXP_TXP5 L32 EXP_TXN6 K32 EXP_TXP6 M36 EXP_TXN7 L36 EXP_TXP7 N32 EXP_TXN8 M32 EXP_TXP8 P36 EXP_TXN9 N36 EXP_TXP9 R32 EXP_TXN10 P32 EXP_TXP10 T36 EXP_TXN11 R36 EXP_TXP11 U32 EXP_TXN12 T32 EXP_TXP12 V36 EXP_TXN13 U36 EXP_TXP13 W32 EXP_TXN14 V32 EXP_TXP14 Y36 EXP_TXN15 W36 EXP_TXP15 Сигналы что сверху уже есть на картинке,а вот сигналы с низу? Table 13-18. Thermal and Power Sequencing Signal Group Ball Signal Ball Signal AE29 RSTIN# F5 THRMTRIP# H10 HCPURST# J21 EXT_TS0# AD30 PWROK H22 EXT_TS1# J23 BM_BUSY# А из этих сигналов, я не знаю какие соответствуют: PRSNT1# PRSNT2# REFCLK- REFCLK+ JTAG3 JTAG4 AD30 PWROK вроде похож на A11 PWRGD но я неуверен. Если кто знает,подскажите пожалуйста.

ДОБАВЛЕНО 15/02/2009 23:37

Извеняюсь что ненаписал сразу, картинка (разьёма PCIe x16) мною была взята с сайта www.thg.ru/ И немного подкоректирована.

Всем доброго дня. О недостающих сигналах,кое-что нарыл в гугле. Но вопросов не убавилось, а именно: 1 Сигналы JTAG3 (JTAG4) — Это сигналы( TDI ) ( TDO ) Входа и Выхода тестовой последовательности. Вопрос—Чего именно? и что за последовательность такая? 2 Сигналы REFCLK + ( — ) — Это Эталонный тактовый сигнал шины. Вопрос — Где их искать? и какая частота? Что это такое ( + ) и ( — ) ? 3 Сигнал PRSNT1# — Это сигнал наличия устройства в слоте. Вопрос — Какого типа этот сигнал? И что означает — # ? 4 Сигнал PRSNT2# — Это сигнал опредиления функциональности устройства. (По линии на сигнал — B17—X1, B31—X4,B49—X8,B81—X16) Вопрос — Опять-же, какой тип сигнала? 5 Сигнал PWRGD Вопрос — Это какое-то дополнительное питание для включения видеокарточки? Или что-то ещё?

И ещё. Исча в инете информацию,я заметил,что некаторые даташиты по сигналам PCIe x16,используют немного другие названия, а именно: PEX_TX0-15# PEX_TX0-15 вместо: EXP_TXN0-15 EXP_TXP0-15 Так вот, я хотел спросить,- Это одинаковые сигналы или разные? и Какой сигнал,какому сигналу соответствует? Заранее спасибо.

Всем доброго вечера. hood Большое спасибо что ответил! А то я начал подозревать что «Меня не слышат — минус; но и негонят — это плюс»И что кроме меня,всех остальных совершенно устраивают их ноутбуки со слабым встроенным видеоядром! (никого нехотел обидеть этой фразой!) (думаю, ПРАВИЛА САЙТА я не нарушил?)

Какие решения стоит ожидать в будущем

В ближайшем будущем ожидается внедрение PCI Express 5.0 и 6.0, которые разработаны под решение задач, требующих максимальной пропускной способности — это работа сетевых технологий, графических процессоров и высоконагруженных систем. Потребность в этих стандартах обусловлена ростом требований к устройствам и необходимостью появления более широких каналов передачи данных в облачных сервисах и крупных ЦОД.

Стандартом PCIe 5.0 поддерживается обратная совместимость с предыдущими версиями, в том числе с PCIe 1.0. Для этого предназначен специальный разъем для карт расширения (CEM). PCI Express 6.0 также будет обратно совместимым с ранними поколениями, однако в случае с PCIe 1.0 станет возможным получение только 4 ГБ/с в одну сторону, от порта x16. Также в версии PCIe 6.0 будет предусмотрена технология PAM4, с помощью которой станет возможной фактическая одновременная передача двух бит данных вместо одного. Несколько байт в каждом пакете данных при этом будут резервироваться, чтобы повысить качество передачи информации, выявлять и исправлять ошибки.

Технологии не стоят на месте и Сервер Гейт шагает в ногу со временем, разобраться и подобрать решения для вашего бизнеса — задача не из легкий, наши профессионалы всегда выслушают нужды клиентов и подберут подходящее серверное оборудование.

Принцип работы PCIe

По аналогии с сетевым протоколом, архитектура PCIe также делится на уровни:

- Application Layer — на этом уровне данные пакетируются и передаются на следующий уровень под заголовком (Header+Data);

- Transaction Layer — на данном уровне полученные блоки информации проверяются на отсутствие искажений (путем сверки их кода с контрольным числом), то есть заголовок (Header+Data) дополняется кодом проверки ECRC (End to End Cyclic Redundancy Check);

- Data Link Layer — этот уровень используется для присвоения пакету уникального двухбайтового номера (Sequence Number), позволяющего сократить риск неудачной транспортировки данных. Также, помимо информации, переданной с предшествующих уровней (Header+Data+ECRC), к блоку прибавляется код LCRC (Local Cyclic Redundancy Check). Он позволяет проверить целостность полученных данных. Если принятая информация прошла проверку LCRC, то источник получает сигнал ACK (ACKnowledge), если передача не произошла, направляется сигнал NAK (Not AcKnowledge), и пакет с Sequence Number передается повторно;

- Physical Layer — на физическом уровне согласовываются условия приема PLP (Physical Layer Packets, необработанных пакетов), определяются параметры полосы — ее ширина и частота для связи с другим устройством.

При поступлении данных с предыдущего уровня информация (Header+Data+ECRC+LCRC) сопровождается стартовым байтом, который уведомляет принимающую сторону о начале блока данных. Завершается этот блок конечным байтом.

Архитектура

Пример топологии PCI Express: белые «распределительные коробки» представляют собой нисходящие порты устройства PCI Express, а серые — восходящие порты.[5]:7 Карта PCI Express x1 с переключателем PCI Express (закрыта небольшой радиатор), который создает несколько конечных точек из одной конечной точки и позволяет нескольким устройствам совместно использовать ее.

Концептуально шина PCI Express представляет собой высокоскоростной серийный замена старой шины PCI / PCI-X.[6] Одно из ключевых отличий шины PCI Express от более старой шины PCI — это топология шины; PCI использует общий параллельно автобус архитектура, в которой хост PCI и все устройства совместно используют общий набор адресов, данных и линий управления. Напротив, PCI Express основан на двухточечной топология, с отдельными серийный ссылки, соединяющие каждое устройство с корневой комплекс (хозяин). Из-за топологии общей шины доступ к старой шине PCI является арбитражным (в случае нескольких мастеров) и ограничивается одним мастером за раз в одном направлении. Более того, старая схема синхронизации PCI ограничивает тактовую частоту шины самым медленным периферийным устройством на шине (независимо от устройств, участвующих в транзакции шины). Напротив, шина PCI Express поддерживает полнодуплексную связь между любыми двумя конечными точками без присущих ограничений на одновременный доступ через несколько конечных точек.

Что касается протокола шины, связь PCI Express инкапсулируется в пакеты. Работа по пакетированию и распаковке данных и трафика сообщений о состоянии выполняется на уровне транзакций порта PCI Express (описанном ниже). Радикальные различия в электрических сигналах и протоколе шины требуют использования другого механического форм-фактора и разъемов расширения (и, следовательно, новых материнских плат и новых плат адаптеров); Слоты PCI и слоты PCI Express не взаимозаменяемы. На программном уровне PCI Express сохраняет Обратная совместимость с PCI; Устаревшее системное программное обеспечение PCI может обнаруживать и настраивать новые устройства PCI Express без явной поддержки стандарта PCI Express, хотя новые функции PCI Express недоступны.

Канал PCI Express между двумя устройствами может иметь размер от одного до 32 переулки. В многополосном канале пакетные данные распределяются по полосам, а пиковая пропускная способность зависит от общей ширины канала. Количество полос автоматически согласовывается во время инициализации устройства и может быть ограничено любой конечной точкой. Например, однополосная карта PCI Express (x1) может быть вставлена в многополосный слот (x4, x8 и т. Д.), И цикл инициализации автоматически согласовывает максимальное количество взаимно поддерживаемых полос. Канал может динамически понижать свою конфигурацию для использования меньшего количества полос, обеспечивая отказоустойчивость в случае наличия плохих или ненадежных полос. Стандарт PCI Express определяет ширину канала x1, x2, x4, x8, x12, x16 и x32.[7] Это позволяет шине PCI Express обслуживать как чувствительные к стоимости приложения, где высокая пропускная способность не требуется, так и приложения, критичные к производительности, такие как трехмерная графика, сетевые (10 Гбит Ethernet или многопортовый Гигабитный Ethernet) и корпоративное хранилище (SAS или Fibre Channel). Слоты и разъемы определены только для подмножества этих значений ширины, при этом между шириной канала используется следующий больший размер физического слота.

Для сравнения: устройство PCI-X (133 МГц, 64 бита) и устройство PCI Express 1.0, использующее четыре полосы (x4), имеют примерно одинаковую пиковую скорость передачи данных в одном направлении, равную 1064 МБ / с. Шина PCI Express потенциально может работать лучше, чем шина PCI-X, в случаях, когда несколько устройств передают данные одновременно или если связь с периферийным устройством PCI Express нарушена. двунаправленный.

Соединить

Канал PCI Express между двумя устройствами состоит из одной или нескольких полос, которые двойной симплекс каналов с использованием двух дифференциальная сигнализация пары.[5]:3

Устройства PCI Express обмениваются данными через логическое соединение, называемое соединять

[8] или

ссылка на сайт

. Связь — это канал связи точка-точка между двумя портами PCI Express, позволяющий им отправлять и получать обычные запросы PCI (конфигурация, ввод-вывод или чтение / запись памяти) и прерывает (INTx, MSI или MSI-X). На физическом уровне ссылка состоит из одного или нескольких

переулки

.[8] Низкоскоростные периферийные устройства (например, 802.11 Wi-Fi карта) используют однополосное соединение (x1), тогда как графический адаптер обычно использует гораздо более широкое и, следовательно, более быстрое соединение с 16 полосами (x16).

полоса дороги

Дорожка состоит из двух дифференциальная сигнализация пары, одна пара для приема данных, а другая для передачи. Таким образом, каждая полоса состоит из четырех проводов или сигнальные следы. Концептуально каждая полоса используется как полнодуплексный байтовый поток, транспортировка пакетов данных в восьмибитном «байтовом» формате одновременно в обоих направлениях между конечными точками ссылки.[9] Физические каналы PCI Express могут содержать от 1 до 16 полос, точнее 1, 4, 8 или 16 полос.[10][5]:4,5[8] Счетчики дорожек записываются с префиксом «x» (например, «x8» обозначает карту или слот с восемью дорожками), причем x16 — это самый большой размер, который обычно используется.[11] Размеры дорожек также обозначаются терминами «ширина» или «через», например, прорезь с восемью полосами движения может называться «на 8» или «шириной 8 полос».

Размеры механических карт см. ниже.

Последовательная шина

| Эта секция не цитировать Любые источники . Пожалуйста помоги улучшить этот раздел от добавление цитат в надежные источники. Материал, не полученный от источника, может быть оспорен и удалено. |

Архитектура связанной последовательной шины была выбрана по сравнению с традиционной параллельной шиной из-за присущих ей ограничений, включая полудуплекс работы, избыточного количества сигналов и, по сути, более низкого пропускная способность из-за временной сдвиг. Синхронизация возникает из-за того, что отдельные электрические сигналы в параллельном интерфейсе проходят через проводники разной длины по потенциально разным печатная плата (PCB) слоев и, возможно, разных скорости сигнала. Несмотря на то, что они передаются одновременно как единый слово, сигналы на параллельном интерфейсе имеют разную продолжительность прохождения и достигают места назначения в разное время. Когда тактовый период интерфейса короче, чем самая большая разница во времени между поступлениями сигнала, восстановление переданного слова больше невозможно. Поскольку временной сдвиг по параллельной шине может составлять несколько наносекунд, результирующее ограничение полосы пропускания находится в диапазоне сотен мегагерц.

Сильно упрощенный

топологии традиционного общего (параллельного) интерфейса PCI и последовательного двухточечного интерфейса PCIe[12]

Последовательный интерфейс не демонстрирует временного сдвига, потому что существует только один дифференциальный сигнал в каждом направлении в каждой полосе, и нет внешнего синхросигнала, поскольку информация синхронизации встроена в сам последовательный сигнал. Таким образом, типичные ограничения полосы пропускания для последовательных сигналов находятся в диапазоне нескольких гигагерц. PCI Express является одним из примеров общей тенденции к замене параллельных шин последовательными межсоединениями; другие примеры включают Последовательный ATA (SATA), USB, Последовательный SCSI (SAS), FireWire (IEEE 1394) и RapidIO. В цифровом видео обычно используются следующие примеры: DVI, HDMI и DisplayPort.

Многоканальный последовательный дизайн увеличивает гибкость за счет возможности выделения меньшего количества полос для более медленных устройств.

Сводка аппаратного протокола

Канал PCIe построен на основе выделенных однонаправленных пар последовательных (1-битных) двухточечных соединений, известных как переулки

. Это резко контрастирует с более ранним соединением PCI, которое представляет собой систему на основе шины, где все устройства используют одну и ту же двунаправленную, 32-битную или 64-битную параллельную шину.

PCI Express — это многоуровневый протокол, состоящий из уровень транзакции

, а

уровень канала передачи данных

, а

физический слой

. Уровень канала передачи данных подразделяется на контроль доступа к медиа Подуровень (MAC). Физический уровень подразделяется на логический и электрический подуровни. Физический логический подуровень содержит подуровень физического кодирования (PCS). Условия заимствованы из IEEE 802 модель сетевого протокола.

Физический слой

Штыри разъема и длина

| Переулки | Булавки | Длина | ||

| Всего | Переменная | Всего | Переменная | |

| 0x1 | 2×18 = 036[87] | 2×07 = 014 | 25 мм | 07,65 мм |

| 0x4 | 2×32 = 064 | 2×21 = 042 | 39 мм | 21,65 мм |

| 0x8 | 2×49 = 098 | 2×38 = 076 | 56 мм | 38.65 мм |

| x16 | 2×82 = 164 | 2×71 = 142 | 89 мм | 71.65 мм |

Открытый разъем PCI Express x1 позволяет подключать более длинные карты, которые используют больше линий, при работе на скорости x1

Физический уровень PCIe (PHY

,

PCIEPHY

,

PCI Express PHY

, или

PCIe PHY

) спецификация разделена на два подуровня, соответствующих электрическим и логическим характеристикам. Логический подуровень иногда дополнительно делится на подуровень MAC и PCS, хотя это разделение формально не является частью спецификации PCIe. Спецификация, опубликованная Intel, PHY-интерфейс для PCI Express (PIPE),[88] определяет функциональное разделение MAC / PCS и интерфейс между этими двумя подуровнями. Спецификация PIPE также определяет

вложение физического носителя

(PMA), который включает сериализатор / десериализатор (SerDes) и другие аналоговые схемы; однако, поскольку реализации SerDes сильно различаются между ASIC поставщиков, PIPE не определяет интерфейс между PCS и PMA.

На электрическом уровне каждая полоса состоит из двух однонаправленных дифференциальные пары работает на 2,5, 5, 8 или 16Гбит/ с, в зависимости от согласованных возможностей. Передача и прием — это отдельные дифференциальные пары, всего четыре провода данных на полосу.

Соединение между любыми двумя устройствами PCIe называется ссылка на сайт

, и состоит из одного или нескольких

переулки

. Все устройства должны минимально поддерживать однополосное (x1) соединение. Устройства могут дополнительно поддерживать более широкие каналы, состоящие из 2, 4, 8, 12, 16 или 32 полос. Это обеспечивает очень хорошую совместимость двумя способами:

- Карта PCIe физически подходит (и работает правильно) в любом слоте, размер которого не меньше ее размера (например, карта размера x1 работает в слоте любого размера);

- Слот большого физического размера (например, x16) может быть электрически подключен к меньшему количеству полос (например, x1, x4, x8 или x12), если он обеспечивает заземляющие соединения, необходимые для большего физического размера слота.

В обоих случаях PCIe согласовывает максимальное количество взаимно поддерживаемых полос. Многие видеокарты, материнские платы и BIOS версии проверены на поддержку подключения x1, x4, x8 и x16 в одном и том же соединении.

Ширина разъема PCIe составляет 8,8 мм, высота — 11,25 мм, а длина может изменяться. Фиксированная часть разъема имеет длину 11,65 мм и содержит два ряда по 11 контактов (всего 22 контакта), а длина другой части может изменяться в зависимости от количества полос. Контакты расположены с интервалом в 1 мм, толщина платы, входящей в разъем, составляет 1,6 мм.[89][90]

Передача информации

PCIe отправляет все управляющие сообщения, включая прерывания, по тем же каналам, которые используются для данных. Последовательный протокол никогда не может быть заблокирован, поэтому время задержки по-прежнему сопоставимо с обычным PCI, который имеет выделенные линии прерывания. Если принять во внимание проблему разделения прерываний на прерываниях на основе выводов и тот факт, что прерывания, сигнализируемые сообщениями, могут обходить APIC ввода-вывода и доставляться напрямую в ЦП, производительность MSI оказывается существенно лучше. [91]

Данные, передаваемые по многополосным каналам, чередуются, что означает, что каждый последующий байт отправляется по последовательным дорожкам. В спецификации PCIe это чередование именуется как чередование данных

. Требуя значительной аппаратной сложности для синхронизации (или выравнивать) входящих данных с чередованием, чередование может значительно уменьшить задержку

п

th байт по ссылке. Хотя полосы не синхронизированы плотно, существует ограничение на

перекос от полосы к полосе

20/8/6 нс для 2,5 / 5/8 ГТ / с, чтобы аппаратные буферы могли повторно выровнять чередующиеся данные.[92] Из-за требований к заполнению чередование может не обязательно уменьшать задержку небольших пакетов данных в канале.

Как и в случае с другими протоколами последовательной передачи с высокой скоростью передачи данных, часы встроенный в сигнале. На физическом уровне PCI Express 2.0 использует Кодирование 8b / 10b схема[44] (линейный код), чтобы гарантировать, что строки последовательных одинаковых цифр (нулей или единиц) ограничены по длине. Это кодирование использовалось для предотвращения потери приемником того, где находятся края битов. В этой схеме кодирования каждые восемь (некодированных) битов полезной нагрузки данных заменяются 10 (закодированными) битами передаваемых данных, вызывая 20% служебных данных в электрической полосе пропускания. Чтобы улучшить доступную пропускную способность, PCI Express версии 3.0 вместо этого использует 128b / 130b кодирование с карабкаться. Кодирование 128b / 130b основано на скремблировании для ограничения длины серии строк с одинаковыми цифрами в потоках данных и обеспечения синхронизации приемника с передатчиком. Это также снижает электромагнитная интерференция (EMI), предотвращая повторение шаблонов данных в передаваемом потоке данных.

Уровень канала передачи данных

Уровень канала данных выполняет три жизненно важные услуги для экспресс-канала PCIe:

- упорядочить пакеты уровня транзакции (TLP), которые генерируются уровнем транзакции,

- обеспечить надежную доставку TLP между двумя конечными точками через протокол подтверждения (ACK и НАК сигнализация), который явно требует воспроизведения неподтвержденных / ошибочных TLP,

- инициализировать и управлять кредитами управления потоком

На передающей стороне уровень канала данных генерирует возрастающий порядковый номер для каждой исходящей TLP. Он служит уникальным идентификационным тегом для каждого передаваемого TLP и вставляется в заголовок исходящего TLP. 32-битный циклическая проверка избыточности код (известный в этом контексте как Link CRC или LCRC) также добавляется в конец каждого исходящего TLP.

На стороне приема LCRC и порядковый номер полученного TLP проверяются на канальном уровне. Если проверка LCRC завершается неудачно (что указывает на ошибку данных), или порядковый номер выходит за пределы допустимого диапазона (непоследовательный от последнего действительного полученного TLP), то неправильный TLP, а также любые TLP, полученные после неправильного TLP, считаются недействительными и отбрасываются. Получатель отправляет сообщение отрицательного подтверждения (NAK) с порядковым номером недопустимого TLP, запрашивая повторную передачу всех TLP, предшествующих этому порядковому номеру. Если полученный TLP проходит проверку LCRC и имеет правильный порядковый номер, он считается действительным. Получатель ссылки увеличивает порядковый номер (который отслеживает последний полученный хороший TLP) и пересылает действительный TLP на уровень транзакции получателя. Сообщение ACK отправляется удаленному передатчику, указывающее, что TLP был успешно получен (и, соответственно, все TLP с прошлыми порядковыми номерами).

Если передатчик принимает сообщение NAK или подтверждение (NAK или ACK) не получено до истечения периода тайм-аута, передатчик должен повторно передать все TLP, для которых отсутствует положительное подтверждение (ACK). За исключением постоянной неисправности устройства или среды передачи, канальный уровень представляет собой надежное соединение с уровнем транзакций, поскольку протокол передачи обеспечивает доставку TLP по ненадежной среде.

В дополнение к отправке и получению TLP, сгенерированных уровнем транзакций, уровень канала данных также генерирует и потребляет DLLP, пакеты уровня канала данных. Сигналы ACK и NAK передаются через DLLP, как и некоторые сообщения управления мощностью и кредитная информация управления потоком (от имени уровня транзакции).

На практике количество неподтвержденных TLP в полете на канале ограничено двумя факторами: размером буфера воспроизведения передатчика (который должен хранить копию всех переданных TLP до тех пор, пока удаленный приемник не подтвердит их подтверждение), и управлением потоком. кредиты, выдаваемые получателем передатчику. PCI Express требует, чтобы все получатели выдавали минимальное количество кредитов, чтобы гарантировать, что канал позволяет отправлять TLP PCIConfig и TLP сообщений.

Уровень транзакций

PCI Express реализует разделенные транзакции (транзакции с запросом и ответом, разделенными по времени), позволяя каналу передавать другой трафик, в то время как целевое устройство собирает данные для ответа.

PCI Express использует управление потоком на основе кредита. В этой схеме устройство объявляет начальную сумму кредита для каждого полученного буфера на своем уровне транзакции. Устройство на противоположном конце ссылки при отправке транзакций на это устройство подсчитывает количество кредитов, которые каждый TLP потребляет со своей учетной записи. Отправляющее устройство может передавать TLP только в том случае, если при этом количество использованных кредитов не превышает его кредитный лимит. Когда принимающее устройство завершает обработку TLP из своего буфера, оно сигнализирует о возврате кредитов отправляющему устройству, что увеличивает лимит кредита на восстановленную сумму. Счетчики кредитов представляют собой модульные счетчики, и для сравнения израсходованных кредитов с лимитом кредита требуется модульная арифметика. Преимущество этой схемы (по сравнению с другими методами, такими как состояния ожидания или протоколы передачи на основе рукопожатия) состоит в том, что задержка возврата кредита не влияет на производительность при условии, что предел кредита не встречается. Это предположение обычно выполняется, если каждое устройство разработано с адекватным размером буфера.

PCIe 1.x часто указывается для поддержки скорости передачи данных 250 МБ / с в каждом направлении на полосу. Этот показатель рассчитан исходя из физической скорости передачи сигналов (2,5гигабод) делится на служебные данные кодирования (10 бит на байт). Это означает, что карта PCIe с шестнадцатью полосами (x16) теоретически способна обеспечить скорость передачи данных 16×250 МБ / с = 4 ГБ / с в каждом направлении. Хотя это верно с точки зрения байтов данных, более значимые вычисления основаны на используемой скорости полезной нагрузки данных, которая зависит от профиля трафика, который является функцией приложения высокого уровня (программного обеспечения) и промежуточных уровней протокола.

Как и другие системы последовательного соединения с высокой скоростью передачи данных, PCIe имеет протокол и накладные расходы на обработку из-за дополнительной устойчивости передачи (CRC и подтверждения). Длительная непрерывная однонаправленная передача (например, типичная для высокопроизводительных контроллеров хранилища) может достигать> 95% от скорости необработанных (линейных) данных PCIe. Эти передачи также больше всего выигрывают от увеличения количества полос (x2, x4 и т. Д.), Но в более типичных приложениях (таких как USB или Ethernet контроллер) профиль трафика характеризуется как короткие пакеты данных с частыми принудительными подтверждениями.[93] Этот тип трафика снижает эффективность соединения из-за накладных расходов из-за синтаксического анализа пакетов и принудительных прерываний (либо в интерфейсе хоста устройства, либо в процессоре ПК). Протокол для устройств, подключенных к тому же печатная плата, он не требует такой же терпимости к ошибкам передачи, как протокол для связи на большие расстояния, и, таким образом, эта потеря эффективности не является специфической для PCIe.

использованная литература

- Mayhew, D .; Кришнан, В. (август 2003 г.). «PCI Express и расширенная коммутация: эволюционный путь к созданию межсоединений следующего поколения». 11-й симпозиум по высокопроизводительным межсоединениям, 2003 г. Труды

. С. 21–29. Дои:10.1109 / CONECT.2003.1231473. ISBN 0-7695-2012-X . S2CID 7456382. - «Определение PCI Express».

- Чжан, Яньминь; Нгуен, Т. Лонг (июнь 2007 г.). «Включить расширенную систему отчетов об ошибках PCI Express в ядре» (PDF). Материалы симпозиума по Linux

. Проект Fedora. Архивировано из оригинал (PDF) 10 марта 2016 г.. Получено 8 мая 2012. - https://www.hyperstone.com Форм-факторы флэш-памяти — основы надежной флэш-памяти, последнее обращение 19 апреля 2022 г.

- ^ абc

Рави Будрук (21 августа 2007 г.). «Основы PCI Express». PCI-SIG. Архивировано из оригинал (PDF) 15 июля 2014 г.. Получено 15 июля 2014. - «Как работает PCI Express». Как это работает

. 17 августа 2005 г. В архиве из оригинала от 3 декабря 2009 г.. Получено 7 декабря 2009. - «4.2.4.9. Согласование ширины линии и последовательности полос», Базовая спецификация PCI Express, редакция 2.1.

, 4 марта 2009 г. - ^ абc

«Часто задаваемые вопросы об архитектуре PCI Express». PCI-SIG. Архивировано из оригинал 13 ноября 2008 г.. Получено 23 ноября 2008. - «Шина PCI Express». Интерфейсная шина

. Архивировано из оригинал 8 декабря 2007 г.. Получено 12 июн 2010. - 32 полосы определяются Базовая спецификация PCIe

но нет стандарта карты в

Электромеханические характеристики карты PCIe

. - «PCI Express — Обзор стандарта PCI Express». Зона разработчика

. Национальные инструменты. 13 августа 2009 г. В архиве из оригинала 5 января 2010 г.. Получено 7 декабря 2009. - Кази, Атиф. «Что такое слоты PCIe?». ПК Gear Lab

. Получено 8 апреля 2022. - «Новый форм-фактор PCIe позволяет более широко использовать твердотельные накопители PCIe». NVM Express

. 12 июня 2012 г. В архиве из оригинала от 6 сентября 2015 г. - «Обзор твердотельного накопителя Memblaze PBlaze4 AIC NVMe». StorageReview

. 21 декабря 2015. - https://www.techradar.com/news/gaming/19-graphics-cards-that-shaped-the-future-of-gaming-1289666

- https://www.eurogamer.net/articles/digitalfoundry-2020-nvidia-geforce-rtx-3080-review

- «Обзор Sapphire Radeon RX 5700 XT Pulse | bit-tech.net». bit-tech.net

. Получено 26 августа 2022. - «AMD Radeon ™ RX 5700 XT 8 ГБ GDDR6 THICC II — RX-57XT8DFD6». xfxforce.com

. Получено 25 августа 2022. - https://rog.asus.com/Graphics-Cards/Graphics-Cards/ROG-Strix/ROG-STRIX-RTX3080-O10G-GAMING-model/spec

- «Какая конфигурация карт PCI на стороне A и стороне B». Часто задаваемые вопросы

. Adex Electronics. 1998. Архивировано с оригинал 2 ноября 2011 г.. Получено 24 октября 2011. - ^ абВерсия 2.0 электромеханических спецификаций карты PCI Express

- «Подсостояния L1 PM с CLKREQ, версия 1.0a» (PDF). PCI-SIG. Получено 8 ноября 2022.

- «Механизм аварийного снижения мощности с ECN сигнала PWRBRK» (PDF). PCI-SIG. Архивировано из оригинал (PDF) 9 ноября 2022 г.. Получено 8 ноября 2022.

- Версия 1.1 электромеханических спецификаций карты PCI Express

- Шенборн, Зале (2004), Рекомендации по проектированию плат для архитектуры PCI Express

(PDF), PCI-SIG, стр. 19–21, в архиве (PDF) из оригинала 27 марта 2016 г. - ^ аб

«Mini-Fit® PCI Express® * Соединительная система проводов к плате» (PDF). Получено 4 декабря 2022. - PCI Express x16 Graphics 150W-ATX Версия 1.0 спецификации

- Плата высокой мощности PCI Express 225 Вт / 300 Вт, редакция 1.0, электромеханические спецификации

- Версия 3.0 электромеханических спецификаций карты PCI Express

- Юнь Лин (16 мая 2008 г.). «Обновления электромеханики PCIe». Архивировано из оригинал 5 ноября 2015 г.. Получено 7 ноября 2015.

- «MP1: адаптер Mini PCI Express / PCI Express». hwtools.net

. 18 июля 2014 г. В архиве из оригинала 3 октября 2014 г.. Получено 28 сентября 2014. - «Часто задаваемые вопросы по mSATA: Основы для начинающих». Обзор ноутбука. В архиве из оригинала 12 февраля 2012 г.

- «Исследование Eee PC». ivc

(вики). В архиве из оригинала 30 марта 2010 г.. Получено 26 октября 2009. - «Совместимость с твердотельными накопителями (SSD) системной платы для настольных ПК». Intel. В архиве из оригинала от 2 января 2016 г.

- «Как различать различия между картами M.2 | Dell США». www.dell.com

. Получено 24 марта 2022. - «Спецификация внешних кабелей PCI Express 1.0». В архиве из оригинала 10 февраля 2007 г.. Получено 9 февраля 2007.

- «Спецификация внешних кабелей PCI Express завершена PCI-SIG». PCI SIG. 7 февраля 2007 г. Архивировано с оригинал 26 ноября 2013 г.. Получено 7 декабря 2012.

- ^ абc

«PCI SIG обсуждает M ‐ PCIe oculink и PCIe 4-го поколения»,

Реестр

, Великобритания, 13 сентября 2013 г., в архиве из оригинала 29 июня 2022 г. - Антон Шилов. PCI SIG завершит разработку внешнего PCI Express OCuLink этой осенью В архиве 2015-06-27 на Wayback Machine. KitGuru. 26 июня 2015 г.

- ^ аб

OCuLink 2-го поколения В архиве 2017-03-13 в Wayback Machine - «Универсальные решения ввода-вывода Supermicro (UIO)». Supermicro.com. В архиве из оригинала 24 марта 2014 г.. Получено 24 марта 2014.

- «Приготовьтесь к тестированию M-PCIe», Дизайн печатной платы

, EDN - «Часто задаваемые вопросы о PCI Express 4.0». pcisig.com

. PCI-SIG. Архивировано из оригинал 18 мая 2014 г.. Получено 18 мая 2014. - ^ абc

«Часто задаваемые вопросы о PCI Express 3.0».

pcisig.com

. PCI-SIG. Архивировано из оригинал 1 февраля 2014 г.. Получено 1 мая 2014. - «Что вообще означает GT / s?». TM World

. В архиве из оригинала 14 августа 2012 г.. Получено 7 декабря 2012. - «Результат 12.2». : Eiscat. Архивировано из оригинал 17 августа 2010 г.. Получено 7 декабря 2012.

- PCI SIG

, в архиве из оригинала 6 июля 2008 г. - «Объявлена спецификация PCI Express Base 2.0» (PDF) (Пресс-релиз). PCI-SIG. 15 января 2007 г. Архивировано с оригинал (PDF) 4 марта 2007 г.. Получено 9 февраля 2007. — обратите внимание, что в этом пресс-релизе термин совокупная пропускная способность

относится к сумме входящей и исходящей пропускной способности; используя эту терминологию, совокупная полоса пропускания полнодуплексного 100BASE-TX составляет 200 Мбит / с. - Смит, Тони (11 октября 2006 г.). «Опубликован окончательный проект спецификации PCI Express 2.0». Реестр

. В архиве из оригинала 29 января 2007 г.. Получено 9 февраля 2007. - Ки, Гэри; Финк, Уэсли (21 мая 2007 г.). «Intel P35: расширяется массовый набор микросхем Intel». АнандТех. В архиве из оригинала 23 мая 2007 г.. Получено 21 мая 2007.

- Хьюнь, Ань (8 февраля 2007 г.). «NVIDIA» MCP72 «Подробности раскрыты». АнандТех. Архивировано из оригинал 10 февраля 2007 г.. Получено 9 февраля 2007.

- «Краткое описание набора микросхем Intel P35 Express» (PDF). Intel. В архиве (PDF) из оригинала 26 сентября 2007 г.. Получено 5 сентября 2007.

- Хахман, Марк (5 августа 2009 г.). «Спецификация PCI Express 3.0 продлена до 2010 года». PC Mag. В архиве из оригинала 7 января 2014 г.. Получено 7 декабря 2012.

- «Пропускная способность PCI Express 3.0: 8,0 гигатрансферов / с». ExtremeTech. 9 августа 2007 г. В архиве из оригинала 24 октября 2007 г.. Получено 5 сентября 2007.

- «Специализированная группа по интересам PCI публикует стандарт PCI Express 3.0». X bit labs. 18 ноября 2010. Архивировано с оригинал 21 ноября 2010 г.. Получено 18 ноября 2010.

- «Раскрыты спецификации PCIe 3.1 и 4.0». eteknix.com

. В архиве из оригинала от 1 февраля 2016 г. - «Кошелек или жизнь… Выпущен PCI Express 3.1!». synopsys.com

. В архиве из оригинала от 23 марта 2015 г. - «Развитие PCI Express 4.0 до 16 ГТ / с, что вдвое превышает пропускную способность технологии PCI Express 3.0» (пресс-релиз). PCI-SIG. 29 ноября 2011. Архивировано с оригинал 23 декабря 2012 г.. Получено 7 декабря 2012.

- https://pcisig.com/faq?field_category_value%5B%5D=pci_express_4.0#4415 В архиве 2016-10-20 на Wayback Machine

- «PCIe 4.0 выходит на рынок, 5.0 — в лабораторию». EE Times

. 26 июня 2016 г. В архиве с оригинала 28 августа 2016 г.. Получено 27 августа 2016. - «IDF: PCIe 4.0 läuft, PCIe 5.0 in Arbeit». Heise Online

(на немецком). 18 августа 2016 г. В архиве с оригинала 19 августа 2016 г.. Получено 18 августа 2016. - ^ аб

Родился Эрик (8 июня 2022 г.). «Наконец-то вышла спецификация PCIe 4.0 со скоростью 16 ГТ / с». Технический отчет. В архиве из оригинала от 8 июня 2022 г.. Получено 8 июн 2022. - https://www.mellanox.com/page/press_release_item?id=1737

- https://www.mellanox.com/page/press_release_item?id=1810

- https://www-03.ibm.com/press/us/en/pressrelease/53452.wss

- «NETINT представляет кодовую плотность с поддержкой PCIe 4.0 — технологии NETINT». NETINT Технологии

. 17 июля 2022 г.. Получено 28 сентября 2022. - https://wccftech.com/amd-ryzen-3000-zen-2-desktop-am4-processors-launching-mid-2019/

- Алькорн, Пол (3 июня 2022 г.). «Поддержка AMD Nixes PCIe 4.0 на старых материнских платах с Socket AM4, и вот почему». Оборудование Тома

. В архиве с оригинала 10 июня 2022 г.. Получено 10 июн 2019. - Алькорн, Пол (10 января 2022 г.). «PCIe 4.0 может быть установлен на всех материнских платах AMD Socket AM4 (обновлено)». Оборудование Тома

. В архиве с оригинала 10 июня 2022 г.. Получено 10 июн 2019. - Катресс, доктор Ян (13 августа 2022 г.). «Тигровое озеро IO и Power». Анандтех

. - «PLDA объявляет о выпуске IP-адреса контроллера XpressRICH5 ™ PCIe 5.0 | PLDA.com». www.plda.com

. Получено 28 июн 2022. - «XpressRICH5 для ASIC | PLDA.com». www.plda.com

. Получено 28 июн 2022. - «Удвоение пропускной способности менее чем за два года: версия 5.0 базовой спецификации PCI Express®, версия 0.9 теперь доступна для участников». pcisig.com

. Получено 12 декабря 2022. - «PCIe 5.0 готов к работе». tomshardware.com

. Получено 18 января 2022. - https://www.businesswire.com/news/home/20190529005766/en/PCI-SIG%C2%AE-Achieves-32GTs-New-PCI-Express%C2%AE-5.0

- https://www.pcgameshardware.de/Mainboard-Hardware-154107/News/PCI-Express50-China-stellt-ersten-Controller-vor-1337072/

- ^ аб

https://www.businesswire.com/news/home/20190618005945/en/PCI-SIG%C2%AE-Announces-Upcoming-PCI-Express%C2%AE-6.0-Specification - https://www.anandtech.com/show/14559/pci-express-bandwidth-to-be-doubled-again-pcie-60-announced-spec-to-land-in-2021

- https://www.phoronix.com/scan.php?page=news_item&px=PCI-Express-6.0-v0.5

- Шилов, Антон. «Спецификация PCIe 6.0 достигла вехи: готов полный проект». Оборудование Тома

. Оборудование Тома. Получено 5 ноября 2022. - «Демонстрация PLX демонстрирует PCIe через оптоволокно как межсоединение кластеризации центра обработки данных». Монтаж кабеля

. Penn Well. Получено 29 августа 2012. - «Представлено второе поколение PCI Express Gen 2 по оптоволоконным системам». Аднако. 22 апреля 2011 г. В архиве из оригинала 4 октября 2012 г.. Получено 29 августа 2012.

- «Активная оптическая кабельная система PCIe». В архиве с оригинала 30 декабря 2014 г.. Получено 23 октября 2015.

- «Acer и Asus представят технологию Intel Thunderbolt Speed на ПК с Windows». Компьютерный мир

. 14 сентября 2011 г. В архиве из оригинала 18 января 2012 г.. Получено 7 декабря 2012. - Кевин Пэрриш (28 июня 2013 г.). «Запуск PCIe для мобильных устройств; раскрыты спецификации PCIe 3.1, 4.0». Оборудование Тома

. Получено 10 июля 2014. - «Спецификации PCI Express 4.0 Draft 0.7 и PIPE 4.4 — Что они значат для разработчиков? — Техническая статья Synopsys | ChipEstimate.com». www.chipestimate.com

. Получено 28 июн 2022. - «Распиновка шины PCI Express 1x, 4x, 8x, 16x @». : Распиновки. В архиве из оригинала 25 ноября 2009 г.. Получено 7 декабря 2009.

- «PHY-интерфейс для архитектуры PCI Express» (PDF) (версия 2.00 ред.). Intel. Архивировано из оригинал (PDF) 17 марта 2008 г.. Получено 21 мая 2008.

- «Механический чертеж разъема PCI Express». Интерфейсная шина. Получено 7 декабря 2007.

- «Схема FCi для разъемов PCIe» (PDF). FCI connect. Получено 7 декабря 2007.

- <

- БАЗОВАЯ СПЕЦИФИКАЦИЯ PCI EXPRESS, РЕД. 3.0

Таблица 4-24 - «Компьютерная периферия и интерфейсы». Технические публикации Пуна. В архиве из оригинала 25 февраля 2014 г.. Получено 23 июля 2009.

- «Все о различных кабелях и разъемах питания ПК». www.playtool.com

. Получено 10 ноября 2022. - «NVIDIA представляет NVIDIA Quadro® Plex — квантовый скачок в визуальных вычислениях». Nvidia

. 1 августа 2006 г. В архиве из оригинала 24 августа 2006 г.. Получено 14 июля 2022. - «Quadro Plex VCS — Расширенная визуализация и удаленная графика». nVidia. В архиве из оригинала 28 апреля 2011 г.. Получено 11 сентября 2010.

- «XGP». ATI

. AMD. Архивировано из оригинал 29 января 2010 г.. Получено 11 сентября 2010. - Выпущен внешний графический процессор Fujitsu-Siemens Amilo GraphicBooster для ноутбуков

, 3 декабря 2008 г., в архиве из оригинала 16 октября 2015 г., получено 9 августа 2015 - Графическая док-станция DynaVivid от Acer прибывает во Францию, а как насчет США?

, 11 августа 2010 г., в архиве из оригинала 16 октября 2015 г., получено 9 августа 2015 - Догерти, Стив (22 мая 2010 г.), «MSI продемонстрирует внешнее графическое решение GUS для ноутбуков на Computex», TweakTown

- Хеллстрем, Джерри (9 августа 2011 г.), «ExpressCard пытается вытащить (не очень) быстрый?», Перспектива ПК

(передовая), в архиве из оригинала на 1 февраля 2016 г. - «PE4H V3.2 (адаптер PCIe x16)». Hwtools.net. В архиве из оригинала 14 февраля 2014 г.. Получено 5 февраля 2014.

- О’Брайен, Кевин (8 сентября 2010 г.), «Как обновить видеокарту ноутбука с помощью DIY ViDOCK», Обзор ноутбука

, в архиве из оригинала 13 декабря 2013 г. - Лал Шимпи, Ананд (7 сентября 2011 г.), «Устройства Thunderbolt просачиваются: Magma’s ExpressBox 3T», АнандТех

, в архиве из оригинала 4 марта 2016 г. - «Внешний корпус для графического процессора MSI GUS II с Thunderbolt». Грани

(руки вверх). В архиве из оригинала 13 февраля 2012 г.. Получено 12 февраля 2012. - «Графика PCI Express, Thunderbolt», Оборудование Тома

- «Шасси M logics M link Thunderbold не поставляется», Engadget

, 13 декабря 2012 г., в архиве с оригинала 25 июня 2022 г. - Бернс, Крис (17 октября 2022 г.), «Подробно о Razer Blade Stealth и Core V2 2017», SlashGear

, в архиве из оригинала 17 октября 2022 г. - «Ассоциация CompactFlash готовит формат XQD следующего поколения, обещает скорость записи 125 МБ / с и выше». Engadget. 8 декабря 2011 г. В архиве из оригинала 19 мая 2014 г.. Получено 18 мая 2014.

- Жолт Керекеш (декабрь 2011 г.). «Что такого особенного в дизайне накопителей Fusion-io ioDrives / PCIe SSD?». storagesearch.com. В архиве из оригинала 23 сентября 2013 г.. Получено 2 октября 2013.

- «Обзор Fusion-io ioDrive Duo Enterprise PCIe». storagereview.com. 16 июля 2012 г. Архивировано с оригинал 4 октября 2013 г.. Получено 2 октября 2013.

- «OCZ Demos 4 TiB, 16 TiB Solid State Drive for Enterprise». X-bit labs. Архивировано из оригинал 25 марта 2013 г.. Получено 7 декабря 2012.

- «Включение приложений высокоскоростного хранения с помощью SATA Express». SATA-IO. В архиве из оригинала 27 ноября 2012 г.. Получено 7 декабря 2012.

- «Карта SATA M.2». SATA-IO. В архиве из оригинала 3 октября 2013 г.. Получено 14 сентября 2013.

- «SCSI Express». Торговая ассоциация SCSI. Архивировано из оригинал 27 января 2013 г.. Получено 27 декабря 2012.

- Медури, Виджай (24 января 2011 г.). «Пример использования PCI Express как высокопроизводительного межсоединения кластера». HPCwire. В архиве из оригинала 14 января 2013 г.. Получено 7 декабря 2012.

- Эван Кобленц (3 февраля 2022 г.). «Новая задержка PCI Express 4.0 может открыть возможности для альтернатив следующего поколения». Tech Republic

. В архиве с оригинала на 1 апреля 2022 г.. Получено 31 марта 2017. - Катресс, Ян. «Выпущена спецификация CXL 1.0: новое отраслевое высокоскоростное соединение от Intel». www.anandtech.com

. Получено 9 августа 2022. - «Список интеграторов | PCI-SIG». pcisig.com

. Получено 27 марта 2022.